You signed in with another tab or window. Reload to refresh your session.You signed out in another tab or window. Reload to refresh your session.You switched accounts on another tab or window. Reload to refresh your session.Dismiss alert

Copy file name to clipboardExpand all lines: README.md

+47-14

Original file line number

Diff line number

Diff line change

@@ -1,10 +1,10 @@

1

1

# SPI MASTER AND SLAVE FOR FPGA

2

2

3

-

The SPI master and SPI slave are simple controllers for communication between FPGA and various peripherals via the SPI interface. The SPI master and SPI slave have been implemented using VHDL 93 and are applicable to any FPGA.

3

+

The [SPI master](#spi-master) and [SPI slave](#spi-slave) are simple controllers for communication between FPGA and various peripherals via the SPI interface. The SPI master and SPI slave have been implemented using VHDL 93 and are applicable to any FPGA.

4

4

5

5

**The SPI master and SPI slave controllers support only SPI mode 0 (CPOL=0, CPHA=0)!**

6

6

7

-

The SPI master and SPI slave controllers were simulated and tested in hardware. I use the GHDL tool for CI: automated VHDL simulations in the GitHub Actions environment ([setup-ghdl-ci](https://github.com/ghdl/setup-ghdl-ci)). If you have a question or you have a tip for improvement, send me an e-mail or create a issue.

7

+

The SPI master and SPI slave controllers were simulated and tested in hardware. I use the GHDL tool for CI: automated VHDL simulations in the GitHub Actions environment ([setup-ghdl-ci](https://github.com/ghdl/setup-ghdl-ci)). If you have a question or an improvement tip, send me an e-mail or create an issue.

8

8

9

9

## SPI master

10

10

@@ -38,9 +38,17 @@ DOUT : out std_logic_vector(WORD_SIZE-1 downto 0); -- received data from SPI

38

38

DOUT_VLD : out std_logic -- when DOUT_VLD = 1, received data are valid

39

39

```

40

40

41

+

### Resource usage:

42

+

43

+

LE | FF | M9K | Fmax

44

+

---|----|-----|-----------

45

+

34 | 23 | 0 | 330.1 MHz

46

+

47

+

*Implementation was performed using Quartus Prime Lite Edition 20.1.0 for Intel Cyclone 10 FPGA (10CL025YU256C8G) with default generics.*

48

+

41

49

### Simulation:

42

50

43

-

A simulation is prepared in the ```sim/``` folder. You can use the prepared TCL script to run simulation in ModelSim.

51

+

A simulation is prepared in the [```sim/```](sim/) folder. You can use the prepared TCL script to run simulation in ModelSim.

44

52

```

45

53

vsim -do spi_master_tb_msim_run.tcl

46

54

```

@@ -76,9 +84,17 @@ DOUT : out std_logic_vector(WORD_SIZE-1 downto 0); -- received data from SPI

76

84

DOUT_VLD : out std_logic -- when DOUT_VLD = 1, received data are valid

77

85

```

78

86

87

+

### Resource usage:

88

+

89

+

LE | FF | M9K | Fmax

90

+

---|----|-----|-----------

91

+

29 | 21 | 0 | 324.5 MHz

92

+

93

+

*Implementation was performed using Quartus Prime Lite Edition 20.1.0 for Intel Cyclone 10 FPGA (10CL025YU256C8G) with default generics.*

94

+

79

95

### Simulation:

80

96

81

-

A simulation is prepared in the ```sim/``` folder. You can use the prepared TCL script to run simulation in ModelSim.

97

+

A simulation is prepared in the [```sim/```](sim/) folder. You can use the prepared TCL script to run simulation in ModelSim.

82

98

```

83

99

vsim -do spi_slave_tb_msim_run.tcl

84

100

```

@@ -88,23 +104,40 @@ Or it is possible to run the simulation using the [GHDL tool](https://github.com

88

104

./spi_slave_tb_ghdl_run.sh

89

105

```

90

106

91

-

## Table of resource usage summary:

107

+

## Examples:

92

108

93

-

CONTROLLER | LE | FF | M9K | Fmax

94

-

:---:|:---:|:---:|:---:|:---:

95

-

SPI MASTER | 34 | 23 | 0 | 334.2 MHz

96

-

SPI SLAVE | 24 | 15 | 0 | 343.7 MHz

109

+

### Spirit Level:

97

110

98

-

*Synthesis have been performed using Quartus Prime 20.1 Lite Edition for FPGA Altera Cyclone IV EP4CE6E22C8 with default generics*

111

+

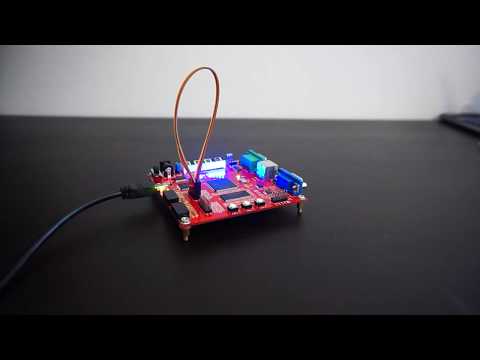

The [Spirit Level example design](examples/spirit_level) shows one possible use of the SPI Master controller. The example design is prepared for [FPGA board CYC1000](https://shop.trenz-electronic.de/en/TEI0003-02-CYC1000-with-Cyclone-10-FPGA-8-MByte-SDRAM) with Intel Cyclone 10 FPGA (10CL025YU256C8G) and [digital accelerometer (LIS3DH)](https://www.st.com/resource/en/datasheet/lis3dh.pdf). Here you can find [the documentation of the CYC1000 board](https://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/Modules_and_Module_Carriers/2.5x6.15/TEI0003/REV02/Documents/CYC1000%20User%20Guide.pdf). In this design, the SPI Master controller is used to configure and read data from the accelerometer. The LEDs on the board show the values from the accelerometer in the form of a spirit level. You can watch the Spirit Level example [video on YouTube](https://youtu.be/EI1BEAkZu5Q).

99

112

100

-

## The SPI loopback example design:

113

+

[](https://youtu.be/EI1BEAkZu5Q)

101

114

102

-

The SPI loopback example design is for testing data transfer between SPI master and SPI slave over external wires.

115

+

###SPI loopback:

103

116

104

-

Please read [README file of SPI loopback example design](examples/loopback/README.md).

117

+

The [SPI loopback example design](examples/loopback) allows testing transfers between SPI master and SPI slave over external wires. The example design is prepared for FPGA board [EP4CE6 Starter Board](http://www.ebay.com/itm/111975895262) with Altera FPGA Cyclone IV (EP4CE6E22C8), few buttons and a seven-segment display (four digit). You can watch the SPI loopback example [video on YouTube](https://youtu.be/-TbtB6Sm2Xk).

105

118

106

119

[](https://youtu.be/-TbtB6Sm2Xk)

107

120

121

+

Display description (from right on board in video):

122

+

123

+

```

124

+

Digit0 = value on SPI slave input

125

+

Digit1 = value on SPI slave output

126

+

Digit2 = value on SPI master input

127

+

Digit3 = value on SPI master output

128

+

```

129

+

130

+

Buttons description (from right on board in video):

131

+

132

+

```

133

+

BTN_ACTION (in mode0) = setup value on SPI slave input

134

+

BTN_ACTION (in mode1) = write (set valid) of SPI slave input value

135

+

BTN_ACTION (in mode2) = setup value on SPI master input

136

+

BTN_ACTION (in mode3) = write (set valid) of SPI slave input value and start transfer between SPI master and SPI slave

137

+

BTN_MODE = switch between modes (mode0 = light decimal point on digit0,...)

138

+

BTN_RESET = reset FPGA design

139

+

```

140

+

108

141

## License:

109

142

110

-

This UART controller is available under the MIT license. Please read [LICENSE file](LICENSE).

143

+

This whole repository (include SPI master and SPI slave controllers) is available under the MIT license. Please read [LICENSE file](LICENSE).

0 commit comments